共计 1696 个字符,预计需要花费 5 分钟才能阅读完成。

提醒:本文最后更新于 2024-08-29 15:02,文中所关联的信息可能已发生改变,请知悉!

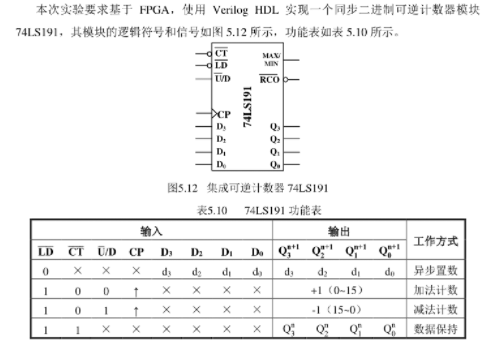

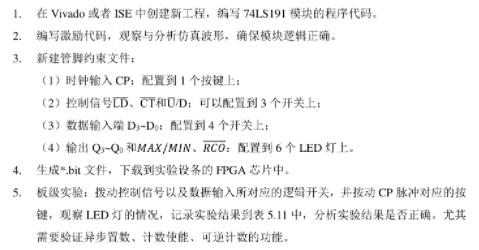

实验要求

实验步骤

74LS191 模块代码

`timescale 1ns / 1ps

module cnt_74LS191(LD_, CT_, U_D, CP, D, Q, Max_Min, RCO_);

input LD_, CT_, U_D, CP;

input [3:0]D;

output [3:0]Q;

output Max_Min, RCO_;

reg [3:0]Q;

reg Max_Min;

reg RCO_;

always @(posedge CP or negedge LD_) begin

if(!LD_) Q <= D;

else if(CT_) Q <= Q;

else begin

if(!U_D) begin

if(Q == 4'b1110) Max_Min <= 1;

else Max_Min <= 0;

Q <= Q + 4'b0001;

end

else begin

if(Q == 4'b0001) Max_Min <= 1;

else Max_Min <= 0;

Q <= Q - 4'b0001;

end

end

end

always @(CP) begin

if(Max_Min == 1 && CP == 0) RCO_ <= 0;

else RCO_ <= 1;

end

endmodule该程序的难点在于,要在合适的时候输出一个 CP 周期的 Max_Min 信号,和在合适的时候(Max_Min信号的后半个周期)输出半个 CP 周期的 RCO_ 信号。(还是要实践出真知)

板极验证

使用的板卡型号:xc7a100tlcsg324-2L

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets LD_]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN V5} [get_ports LD_]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN T4} [get_ports CT_]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN V6} [get_ports U_D]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets CP]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN U18} [get_ports CP]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN U16} [get_ports {D[0]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN R15} [get_ports {D[1]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN V15} [get_ports {D[2]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN T14} [get_ports {D[3]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN U6} [get_ports {Q[3]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN R5} [get_ports {Q[2]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN U7} [get_ports {Q[1]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN R6} [get_ports {Q[0]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN R7} [get_ports Max_Min]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN U8} [get_ports RCO_]在实际实验中,可能会出现,在操作者“自认为的一个周期”(按一下 CP 按键)内,计数器 +/- 的值为 2,甚至可能是 3,这些可能是由于按键抖动造成的(按键消抖还没学,流下了菜菜的泪水)。

正文完