共计 4772 个字符,预计需要花费 12 分钟才能阅读完成。

提醒:本文最后更新于 2024-08-28 14:47,文中所关联的信息可能已发生改变,请知悉!

详细实验部分:https://gcc.lv/2021/10/29/20211029-dc-adder/

一、实验目的与要求

1、实验目的:

(1)掌握全加器、串行进位加法器和超前进位加法器的原理与设计方法;

(2)掌握运用 Verilog HDL 语言进行结构、数据流描述与建模方法;

(3)掌握运用 Verilog HDL 语言进行模块调用的方法。

2、实验要求:

(1)使用结构描述方式建模全加器 FA 模,并仿真验证其功能。

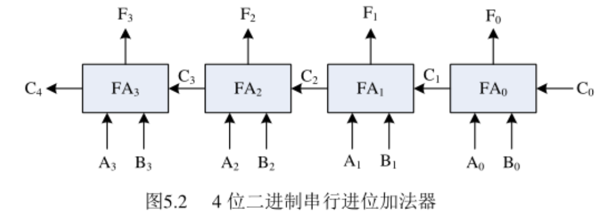

(2)调用 4 个 FA 模块,实现 4 位串行进位加法器(如图 5.2),并仿真验证其功能。

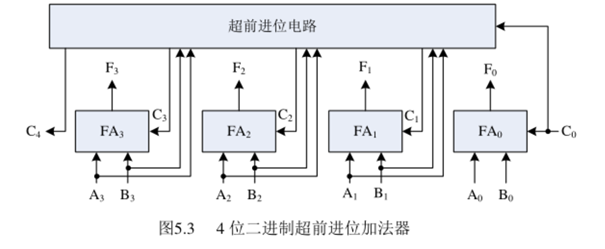

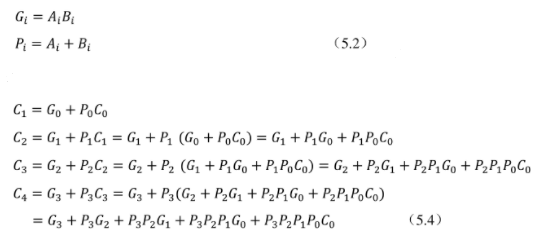

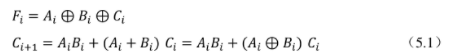

(3)使用数据流描述方法,实现图 5.3 中的 4 位超前进位电路模块,逻辑表达式如式 (5.2) 和式(5.4)。

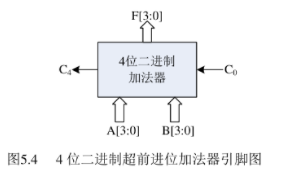

(4)调用 4 个 FA 模块,及 1 个 4 位超前进位电路模块,构成 4 位的超前进位加法器模块。模块引脚如图 5.4 所示, 内部结构如图 5.3 所示。

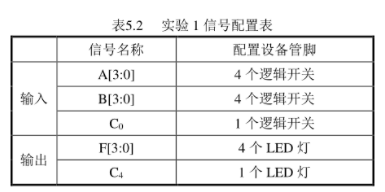

(5)板级验证 4 位二进制超前进位加法器模块。如图。

(6)选择典型输入数据,将实验结果记录到表中

(7)撰写实验报告。

二、实验设计与程序代码

1、模块设计说明

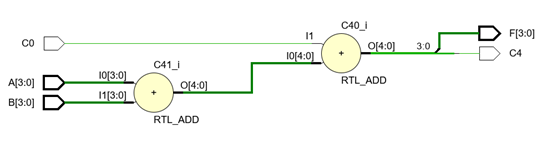

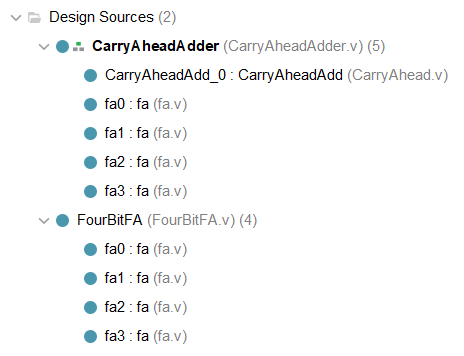

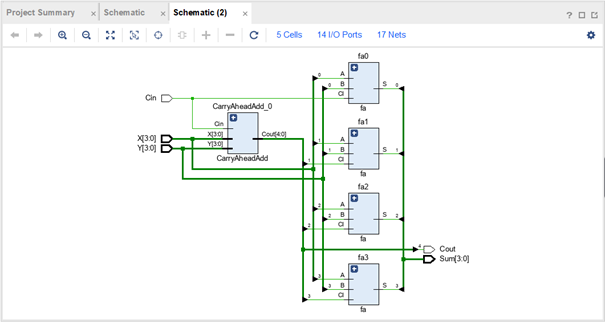

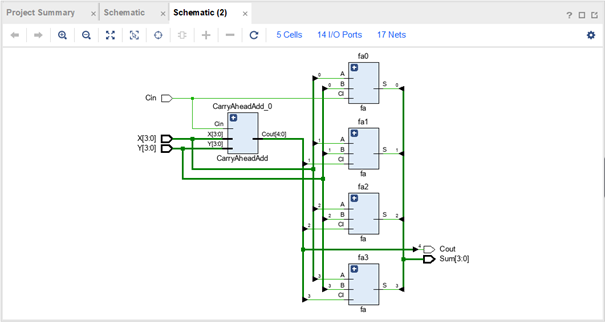

本实验的设计方案完全按照实验要求,分为全加器模块 fa、4 位串行加法器FourBitFA、4 位超前进位电路模块CarryAheadAdd 和 4 位超前进位加法器模块CarryAheadAdder,连接关系如上图所示。

2、实验程序源代码及注释等

// 使用结构建模方式建模全加器 FA 模块

`timescale 1ns / 1ps

module fa(A, B, CI, S, CO);

output S, CO;

input A, B, CI;

wire S1, T1, T2, T3;

xor XOR_1(S1, A, B), //S1 = A 异或 B

XOR_2(S, S1, CI); //S = S1 异或 CI

and AND_1(T1, A, B), //T1 = AB

AND_2(T2, S1, CI); //T2 = S1CI

or OR_1(CO, T1, T2); //S = T1 + T2

endmodule// 4 位串行进位加法器

`timescale 1ns / 1ps

module FourBitFA(X, Y, Cin, Sum, Cout);

parameter size = 4;

input [size-1:0] X, Y;

output [size-1:0] Sum;

input Cin;

output Cout;

wire [size-1:1] C;

//fa(A, B, CI, S, CO);

fa fa0(X[0], Y[0], Cin, Sum[0], C[1]),

fa1(X[1], Y[1], C[1], Sum[1], C[2]),

fa2(X[2], Y[2], C[2], Sum[2], C[3]),

fa3(X[3], Y[3], C[3], Sum[3], Cout);

endmodule// 4 位超前进位电路

`timescale 1ns / 1ps

module CarryAheadAdd(X, Y, Cin, Cout);

parameter size = 4;

input [size-1:0] X, Y;

input Cin;

// output [size-1:0] Sum;

output [size:0] Cout;

wire [size:0] C, G, P;

assign C[0] = Cin;

assign P = X ^ Y;

assign G = X & Y;

assign C[1] = G[0] | (P[0] & C[0]);

assign C[2] = G[1] | (P[1] & (G[0] | (P[0] & C[0])));

assign C[3] = G[2] | (P[2] & (G[1] | (P[1] & (G[0] | (P[0] & C[0])))));

assign C[4] = G[3] | (P[3] & (G[2] | (P[2] & (G[1] | (P[1] & (G[0] | (P[0] & C[0])))))));

// assign Sum = P ^ C[3:0];

assign Cout = C;

endmodule// 4 位超前进位加法器

`timescale 1ns / 1ps

module CarryAheadAdder(Sum, Cout, X, Y, Cin);

parameter size = 4;

input [size-1:0] X, Y;

input Cin;

output [size-1:0] Sum;

output Cout;

wire [size:0] C;

//CarryAheadAdd(X, Y, Cin, Cout);

CarryAheadAdd CarryAheadAdd_0(X, Y, Cin, C);

//fa(A, B, CI, S, CO);

fa fa0(X[0], Y[0], Cin, Sum[0]),

fa1(X[1], Y[1], C[1], Sum[1]),

fa2(X[2], Y[2], C[2], Sum[2]),

fa3(X[3], Y[3], C[3], Sum[3]);

assign Cout = C[4];

endmodule三、实验仿真

1. 仿真代码及结果

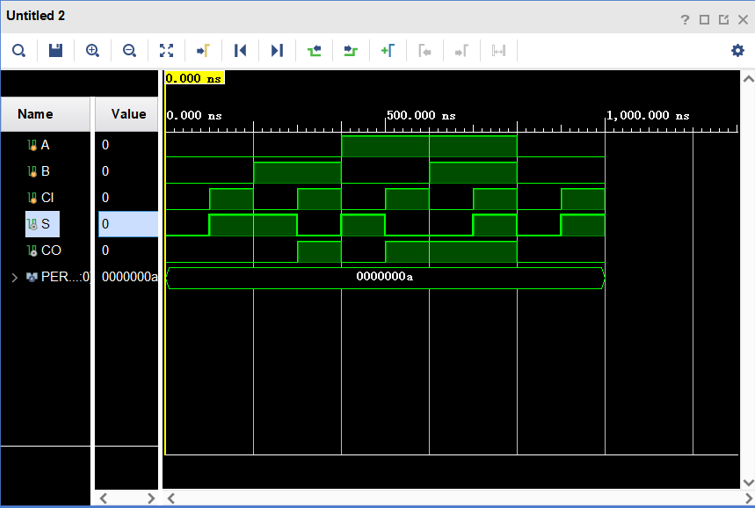

(1)全加器

//~ `New testbench

`timescale 1ns / 1ps

module tb_fa;

// fa Parameters

parameter PERIOD = 10;

// fa Inputs

reg A = 0 ;

reg B = 0 ;

reg CI = 0 ;

// fa Outputs

wire S ;

wire CO ;

fa u_fa (.A ( A),

.B (B),

.CI (CI),

.S (S),

.CO (CO)

);

initial

{A,B,CI}=3'b0;

always

begin

#100;

{A,B,CI}={A,B,CI} + 1'b1;

end

endmodule

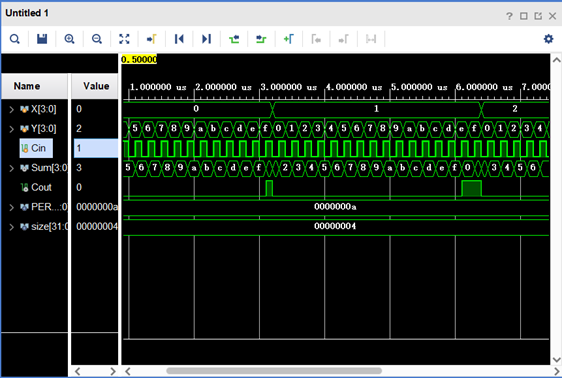

(2)四位串行加法器

//~ `New testbench

`timescale 1ns / 1ps

module tb_FourBitFA;

// FourBitFA Parameters

parameter PERIOD = 10;

parameter size = 4;

// FourBitFA Inputs

reg [size-1:0] X = 0 ;

reg [size-1:0] Y = 0 ;

reg Cin = 0 ;

// FourBitFA Outputs

wire [size-1:0] Sum ;

wire Cout ;

FourBitFA #(.size ( size))

u_FourBitFA (.X ( X [size-1:0] ),

.Y (Y [size-1:0] ),

.Cin (Cin),

.Sum (Sum [size-1:0] ),

.Cout (Cout)

);

initial

{X, Y, Cin} = 9'b0;

always

begin

#100;

{X, Y, Cin} = {X, Y, Cin} + 1'b1;

end

endmodule

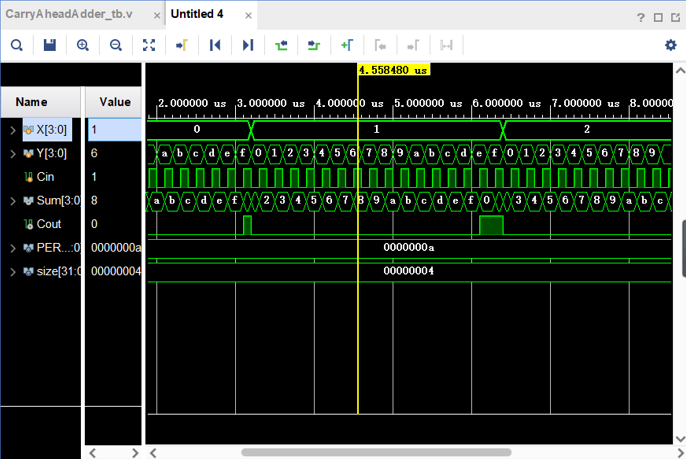

(3)四位超前进位加法器

//~ `New testbench

`timescale 1ns / 1ps

module tb_CarryAheadAdder;

// CarryAheadAdder Parameters

parameter PERIOD = 10;

parameter size = 4;

// CarryAheadAdder Inputs

reg [size-1:0] X = 0 ;

reg [size-1:0] Y = 0 ;

reg Cin = 0 ;

// CarryAheadAdder Outputs

wire [size-1:0] Sum ;

wire Cout ;

CarryAheadAdder #(.size ( size))

u_CarryAheadAdder (.X ( X [size-1:0] ),

.Y (Y [size-1:0] ),

.Cin (Cin),

.Sum (Sum [size-1:0] ),

.Cout (Cout)

);

initial

{X, Y, Cin} = 9'b0;

always

begin

#100;

{X, Y, Cin} = {X, Y, Cin} + 1'b1;

end

endmodule

2. 仿真结果分析

(1)全加器

列举部分例子:

| A | B | CI | S | CO |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

对于有限的仿真结果来说,基本正确,符合要求。

(2)四位串行加法器

| X[3:0] | Y[3:0] | Cin | Sum[3:0] | Cout |

|---|---|---|---|---|

| 0 | 5 | 0 | 5 | 0 |

| 0 | 5 | 1 | 6 | 0 |

| 0 | f | 0 | f | 1 |

| 1 | e | 1 | 0 | 1 |

| 2 | 4 | 0 | 6 | 0 |

| 2 | 9 | 1 | c | 0 |

| 2 | c | 0 | e | 0 |

| 2 | f | 0 | 1 | 1 |

对于有限的仿真结果来说,基本正确,符合要求。

(3)四位超前进位加法器

| X[3:0] | Y[3:0] | Cin | Sum[3:0] | Cout |

|---|---|---|---|---|

| 0 | 5 | 0 | 5 | 0 |

| 0 | 5 | 1 | 6 | 0 |

| 0 | f | 0 | f | 1 |

| 1 | e | 1 | 0 | 1 |

| 2 | 4 | 0 | 6 | 0 |

| 2 | 9 | 1 | c | 0 |

| 2 | c | 0 | e | 0 |

| 2 | f | 0 | 1 | 1 |

对于有限的仿真结果来说,基本正确,符合要求。

四、电路图

五、引脚配置

# X,Y,Cin 依次配置在从左往右的 9 个开关上

# Sum,Cout 依次配置在从左往右的 5 个显示灯上

set_property IOSTANDARD LVCMOS18 [get_ports {X[3]}]

set_property PACKAGE_PIN V5 [get_ports {X[3]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN T4} [get_ports {X[2]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN V6} [get_ports {X[1]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN T5} [get_ports {X[0]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN T6} [get_ports {Y[3]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN V7} [get_ports {Y[2]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN R8} [get_ports {Y[1]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN U9} [get_ports {Y[0]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN T9} [get_ports Cin]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN U6} [get_ports {Sum[3]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN R5} [get_ports {Sum[2]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN U7} [get_ports {Sum[1]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN R6} [get_ports {Sum[0]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN R7} [get_ports Cout]六、思考与探索

1、实验结果记录:

| A[3:0] | B[3:0] | C0 | F[3:0] | C4 |

|---|---|---|---|---|

| 0000 | 0000 | 0 | 0000 | 0 |

| 0000 | 0000 | 1 | 0001 | 0 |

| 1111 | 0000 | 1 | 0000 | 1 |

| 1110 | 0010 | 1 | 0001 | 1 |

| 1111 | 1111 | 1 | 1111 | 1 |

| 1111 | 1111 | 0 | 1110 | 1 |

| 1001 | 1101 | 1 | 0111 | 1 |

| 0100 | 1010 | 1 | 1111 | 0 |

2、实验结论:

通过有限的测试结果,该加法器设计正确。

3、问题与解决方案:

问题:综合时失败,最后发现是因为杀毒软件杀死了进程。

解决方案:在杀毒软件信任 vivado 的运行程序。

4、思考题:

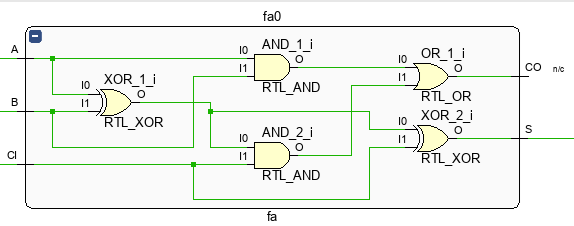

(1)FA 模块的电路图与逻辑表达式是否相符?

相符,如下图

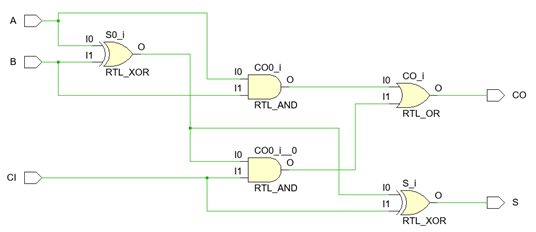

(2)数据流描述方式实现的 FA 与结构建模产生的电路图是否相同

数据流描述:

结果与上面结构建模的电路图相同

(3)4 位串行进位加法器,产生正确的和与进位需要?,如果位数位 n,则为?

9Ty,(2n+1)Ty

(4)得到的电路图与我想设计的相同

(5)assign {C4, F} = A + B + C0;

这种写法生成的电路图不同